El uso de núcleos híbridos, basados en la combinación de núcleos de CPU de diferentes tamaños, consumos y potencia es casi una realidad. Las arquitecturas que los utilizarán ya se encuentran en la rampa de lanzamiento o en avanzado estado de desarrollo. ¿Cómo afectan los núcleos híbridos a las futuras arquitecturas de Intel y AMD?

Hasta ahora las CPU o la parte encargada de las mismas en las APU de Intel y AMD por lo general utilizan configuraciones homogéneas, lo que se traduce en que todo los núcleos son simétricos. Pero sabemos que tanto Intel como AMD apostarán por configuraciones heterogéneas, basadas en una configuración asimétrica de núcleos. Esto significan cambios importantes también en la infraestructura

Núcleos híbridos en futuras arquitecturas de CPU

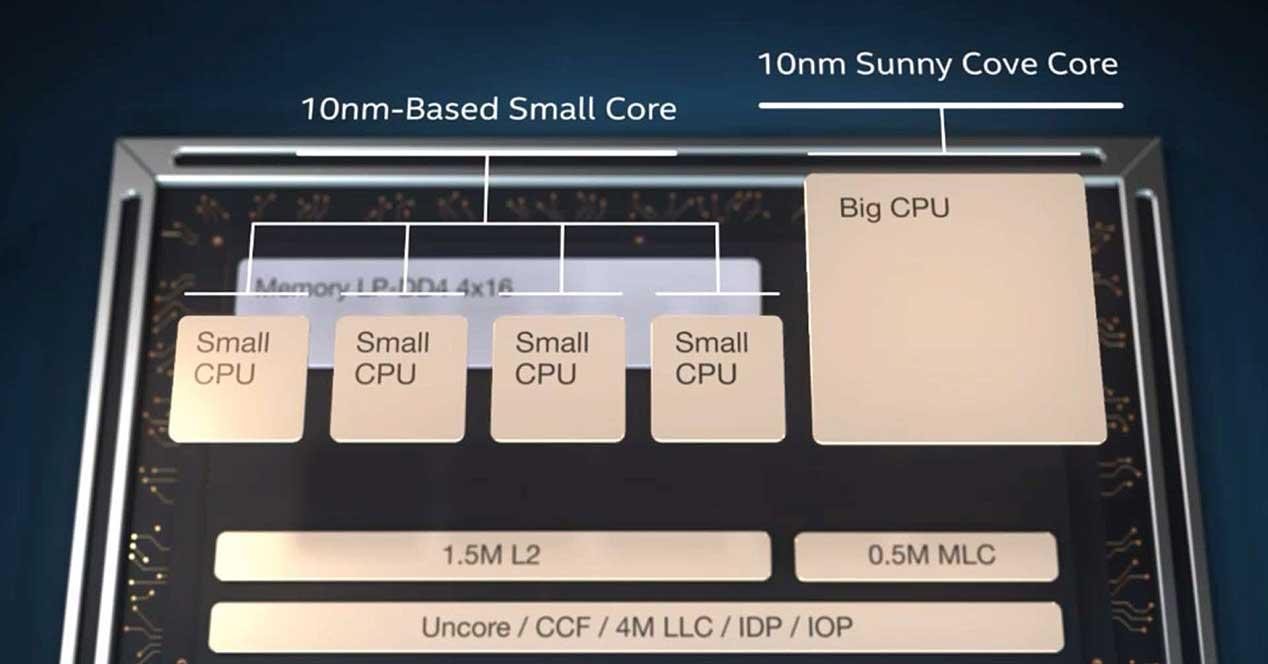

Sabemos que tanto AMD como Intel van a implementar configuraciones híbridas en sus CPU, lo que se traduce en un sistema parecido al DynamiQ de ARM, pero en CPUs con ISA x86. La idea no es otra que acompañar a los núcleos convencionales con otros núcleos más sencillos y por tanto de menor tamaño y consumo. ¿Su utilidad? A día de hoy los PCs tienen una enorme cantidad de tareas activas en segundo plano que restan recursos y potencia a los núcleos más grandes y que se van a beneficiar del añadido de los núcleos más ligeros.

Debido al pequeño tamaño de estos núcleos implementarlos en grandes cantidades es mucho más fácil que aumentar dentro de los futuros procesadores los núcleos convencionales. Por ejemplo, según los rumores sabemos que de Alder Lake-S a Raptor Lake-S Intel no aumentará la cantidad de núcleos con nombre terminado en Cove que son los más potentes, pero si los núcleos Gracemont que son los núcleos ligeros. En el caso de AMD tendremos que esperar más tiempo y

El aumentar la cantidad de núcleos o de otro tipo de componentes supone el aumento de la cantidad de canales de comunicación, los cuales en la arquitectura de un SoC suponen que la parte central del mismo aumento a niveles considerables. Hasta el punto que en muchos diseños ha sido necesario dividir una CPU entera en varios componentes distintos. Tanto de forma asimétrica, en el caso de AMD desde Zen 2, como simétrica, que Intel estrenará con Sapphire Rapids primero en servidores y Meteor Lake después.

¿Cómo se comunican varios núcleos entre sí?

A día de hoy todos los procesadores que hay en el mercado se pueden considerar un SoC, si somos exigentes desde el punto de vista de la arquitectura. El motivo es que tenemos los diferentes componentes del SOC comunicados entre sí a través del componente central que es el Northbridge. El cual va creciendo en complejidad cuantas más componentes ha de comunicar entre sí y más datos ha de transmitir entre ellos

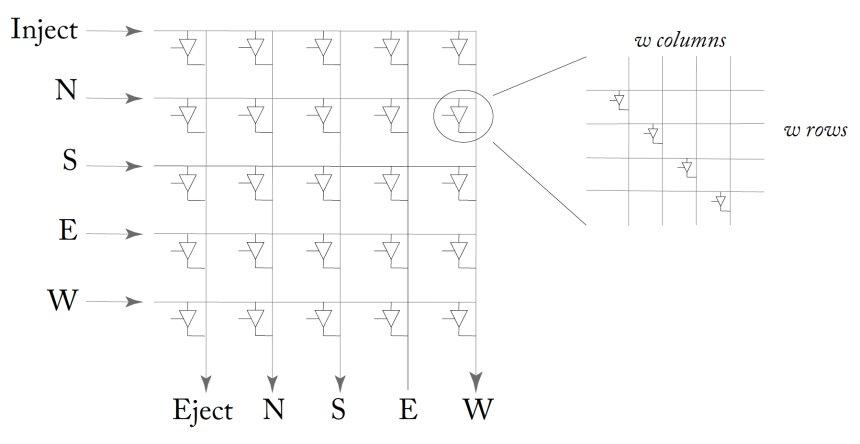

El Northbridge integrado en la mayoría de SoCs, aparte de llevar incorporados una serie de mecanismos de función fija relacionados con los protocolos de comunicación con la memoria RAM y los periféricos, utilizan una interfaz en malla para la comunicación entre los diferentes elementos.

¿Cómo funciona dicha interfaz? Pues muy simple, tenemos una cantidad determinada de componentes conectados entre ellos a través de la interfaz en malla en el Northbridge. Por lo que si tenemos N elementos, entonces habrá N^2 interfaces. Con lo cual se concluye por lógica que a medida que aumenta tanto la cantidad de componentes como el ancho de banda necesario para estos también aumenta el tamaño del Northbridge al aumentar el tamaño del Crossbar

Las CPU con núcleos híbridos significarán un aumento en la cantidad de núcleos considerable. Lo que se traducirá en un aumento en la cantidad de interconexiones. Aunque para esto ya tenemos la solución en forma de la implementación de controladores de red inteligentes en el Northbridge. Lo que hará evolucionar los SoCs de toda la vida en NoCs con el objetivo de soportar de manera más eficiente no solo el creciente número de núcleos, sino también para gestionar de manera más eficiente la comunicación interna dentro del procesador.

Fuente: HardZone