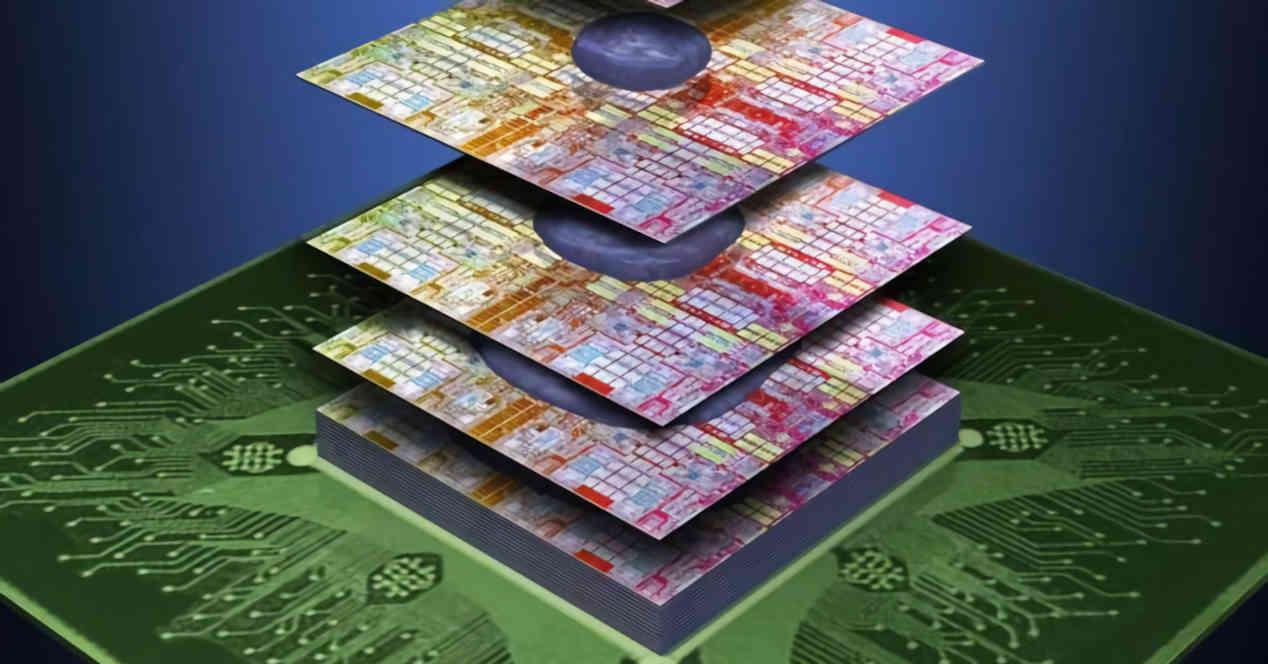

En el primer caso podemos hablar de la V-Cache que AMD ha integrado recientemente en los CCD Chiplet de Zen 3 o la SRAM que Samsung presentó el año pasado. En el caso de lógica+lógica tenemos a los Lake Field de Intel. ¿El último hito? Han conseguido crear un chip 3DIC con lógica integrada y de 4 capas. Os contamos los detalles.

La idea de apilar varios chips e interconectarlos en vertical 3DIC, en el mercado ya la hemos visto en forma de las memoria HBM, pero el hecho de unificar memoria y lógica en un diseño 3DIC o incluso varias capas de chips basados en la lógica es mucho más difícil. Mientras que en el caso de la memoria HBM hemos visto diseños de hasta 4 chips apilados, en el caso de la lógica+memoria o lógica+lógica hemos visto solo composiciones de dos chips.

Consiguen apilar hasta 4 capas de chips en un diseño 3DIC

Aunque con la memoria HBM que se encuentra en las tarjetas gráficas de alto rendimiento ya utiliza una configuración de 4 capas, todas de memoria, el Instituto Estadounidense de Microelectronics, el IMC, ha conseguido un hito tecnológico que permite que hasta 4 capas de chips o semiconductores puedan ser apiladas formando un solo chip en una configuración 3DIC de cuatro capas.

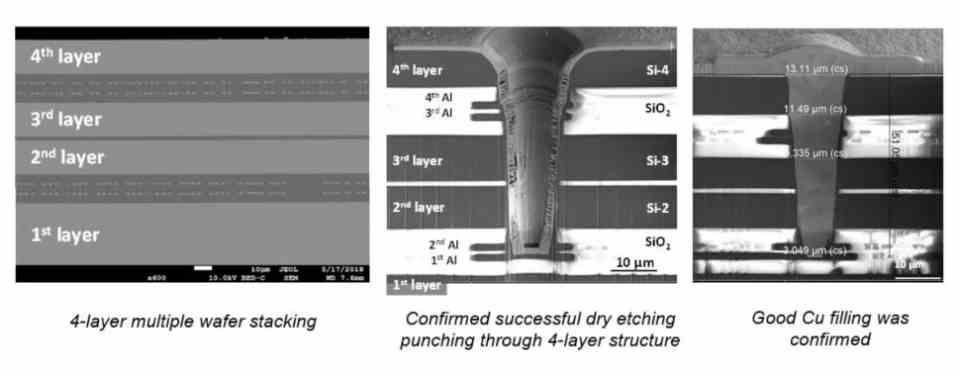

El planteamiento que propone el IME se basa en combinar un par de obleas frente a frente, de tal manera que ambas se conectan por el mismo lado, al cual vamos a llamar A. Para luego conectar los otros dos chips en los extremos pero conectados la cara reversa o B. Una vez se ha hecho este procedimiento, se crean canales para que las vías a través de silicio atraviesen los cuatro chips, permitiendo así la interconexión entre los cuatro chips que forman la composición 3DIC.

El problema de una pila de chips es el ahogamiento termal entre los diferentes chips, el cual se vuelve más complejo a medida que la pila se va haciendo más grande en lo que a su número de componentes se refiere. Es por ese motivo que por ejemplo la memoria HBM 3 no ha visto aún la luz debido al debate interno sobre si aumentar la cantidad de chips a menor velocidad y con ello el ancho del bus o la velocidad del bus en sí misma. En ambos planteamientos el desafío es el mismo, la temperatura.

¿Será adoptado por Intel y/o AMD?

Pues no lo sabemos, por el momento la apuesta de Intel y AMD parece ser por sistemas 2.5DIC en los que varios chips están conectados en un interposer común, algunos de ellos son chips clásicos y los otros son 3DIC. Por el momento tanto AMD como Intel no tienen pensado utilizar vías a través de silicio, sino lo que se llama Silicon Bridges o Puentes de Silicio, al menos para conectar los diferentes componentes del MCM sobre el interposer.

Otra cosa distinta es la composición en vertical, el hecho de añadir hasta 4 chips permite un concepto cuanto menos interesante. El cual consistiría que al igual que el Lakefield separar el Chipset o Southbridge del resto de la CPU por un lado, por el otro se basaría en el añadido de caché de último nivel adicional en una o las dos capas restantes. El aumento de la caché de último nivel gracias al 3DIC es crucial de cara al rendimiento en ciertas aplicaciones que requieren tanto ancho de banda como capacidad de memoria. Donde la solución normalmente es utilizar complejos sistemas de memoria HBM cómo llevarán los futuros Sapphire Rapids de Intel.

Fuente: HardZone