En un viernes como hoy, en pleno mes de agosto, qué mejor que refrescarnos con una noticia sobre los nuevos procesadores de AMD con arquitectura Zen 3. Una nueva filtración pone algo más de luz sobre las especulaciones que llevamos meses escuchando y de paso, muestra los primeros datos relativos a los códigos OPN de varias muestras de ingeniería. ¿Ganas de Ryzen 5000? Seguro que sí.

El hype comienza a crecer con estos Ryzen 5000, no podemos esconderlo, y es que tenemos muchas esperanzas puestas en lo que debe ser el paso definitivo de AMD para competir de tú a tú con Intel en todos los entornos y segmentos del mercado, sin excepción alguna.

Zen 3 será una evolución natural de Zen 2, pero esto no implica que las mejoras sean menores, más bien al contrario. Se van a corregir o al menos paliar la gran mayoría de problemas derivados con latencias internas y de RAM, aparte de las consecuentes mejoras en front end y back end. El primer paso se confirma hoy: modificación de la estructura y matrices entre CCD y CCX.

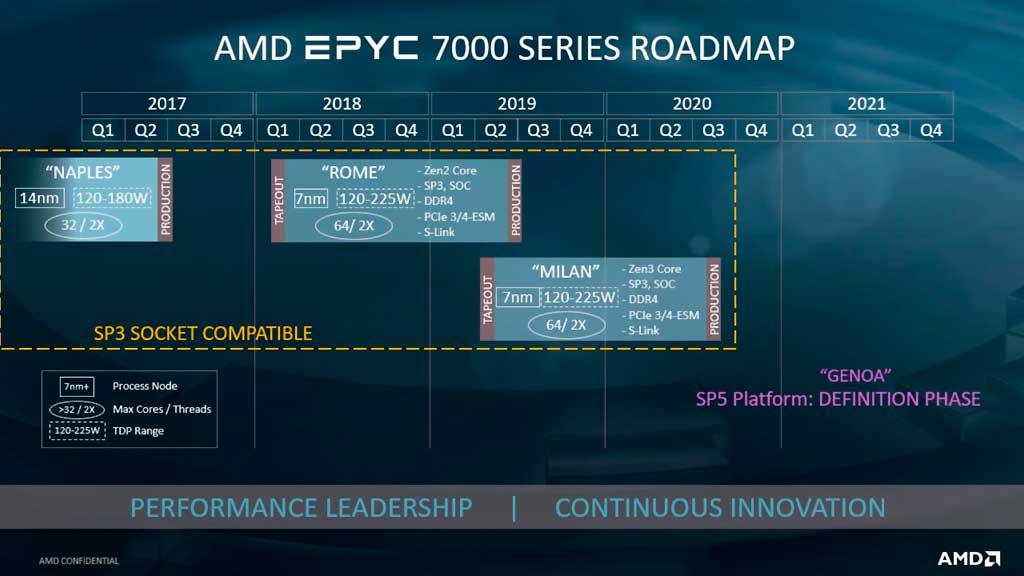

De nuevo EPYC con Milan marca el camino en Zen 3

La jerarquía y diseño de Zen 3 van a ser una serie de apuestas muy interesantes y aunque los datos caen con cuentagotas y se está llevando todo de forma muy discreta, el primer y más importante paso para aumentar el rendimiento y acabar con los problemas se acaba de confirmar por parte de Patrick Shur.

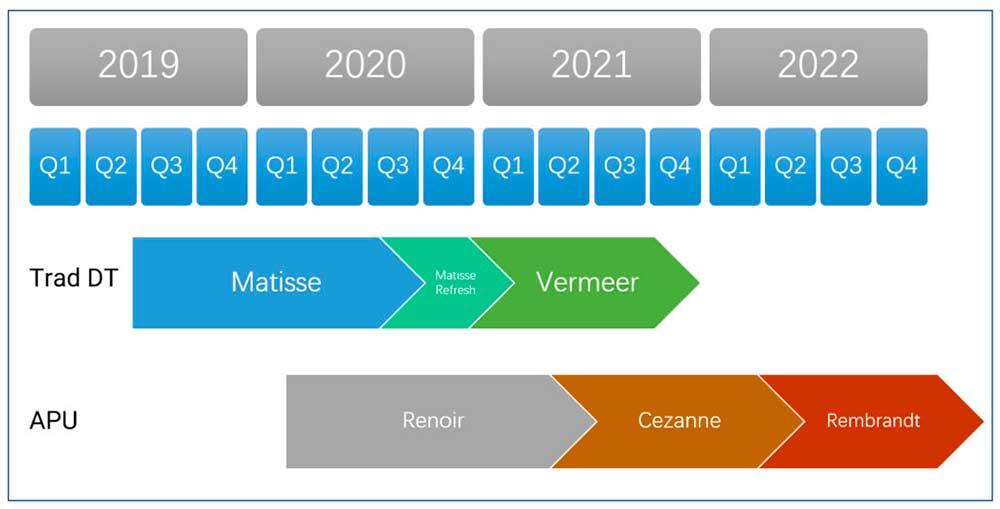

Hay que tener en cuenta desde donde partimos, ya que tanto los Ryzen 4000 Renoir como los Ryzen 3000 Matisse tienen diseños monolíticos en cuanto a matrices se refiere. Como bien sabemos cada matriz incluye varios CCD y dentro de cada uno de ellos tenemos de forma inequívoca dos CCX.

Cada CCX tiene su propia caché L3, la cual no es compartida intrínsecamente dentro del CCD ya que partimos de dos segmentos de L3 de 16 MB y aquí está uno de los principales problemas de Zen 2, ya que según la propia AMD la latencia creció en post de otras mejoras de la arquitectura para dar unas cifras de entre 35 y 40 ciclos por segundo.

Cada CCX puede obtener hasta 4 núcleos, para hacer en total por CCD 8 núcleos y de ahí seguir añadiendo en el PCB principal más de estos para sumar núcleos totales. ¿Cómo se va a gestionar esto en Zen 3?

AMD Ryzen 5000: simplificación de la jerarquía y reducción de la latencia general

Lo simple suele funcionar mejor que lo realmente complicado y por norma, genera menos problemas. Esta parece ser la filosofía que va a usar AMD en Zen 3, ya que según se informa y ya especulábamos, esta arquitectura tendrá una configuración de 8 núcleos con caché L3 unificada por cada CCX.

Esto deja un panorama totalmente diferente de cara a los procesadores, ya que al no usar un proceso litográfico mucho más avanzado que permita implementar muchos más transistores por mm2, AMD podría prescindir directamente del término CCD y hablar directamente de CCX.

¿Por qué? Simple, no podrían aumentar el número de núcleos ni en EPYC ni en Ryzen, ergo el tope estaría en 64 núcleos y 128 hilos, pero aumentando el número de núcleos por CCX no es necesario usar dos de ellos por CCD, sino simplemente tendríamos un CCX con 8 núcleos en vez de dos con 4 de ellos, así que la jerarquía y el uso de CCD carece de sentido en un principio.

Aunque esto no está confirmado y son puras especulaciones, tienen sentido evidentemente, pero al mismo tiempo no se habla de otro tema importante: el tamaño de la L3, ¿mantendrá AMD el mismo tamaño? No hay ni siquiera rumores de esto, pero la simplificación deja claro que podría o mantenerse o reducirse, principalmente por la dependencia del resto de mejoras de la arquitectura.

Ampliarse es poco probable debido al costo monetario y desde el punto de vista de la arquitectura, tendría que haber cambios bastante profundos para que ocurriese y aunque no es descartable, es poco probable.

AMD Cezanne enseña la patita, stepping A0 con 8 núcleos

Los primeros detalles sobre el primer procesador para portátiles ya están aquí, y aunque son escasos, son igualmente interesantes. El chip llega con un código OPN 100-000000285-30_Y donde se informa que estamos antes un procesador de 8 núcleos y 16 hilos que está certificado bajo un stepping A0 con una frecuencia de 3 GHz en Boost.

Nuevos rumores también indican que AMD seguirá su estrategia en portátiles con su socket estrella FP6, así que de nuevo volveremos a ver SP3, AM4 y el nombrado FP6 bajo los mismos parámetros básicos de arquitectura. Esto implicaría que las APU en esta ocasión no tendrán que disponer de cambios importantes como los Ryzen 4000, lo que debería implicar una llegada al mercado más temprana.

Mismo camino siguen los EPYC Milan para servidor, donde también se ha mostrado el primer procesador y su código OPN 100-000000114-07_22 / 15_N, por lo que estamos ante una CPU con un clock base de 1,5 GHz y un Boost de 2,2 GHz para sus 64 núcleos y 128 hilos. También se informa de que ha sido vista en una configuración dual socket para hacer con ello 128 núcleos y 256 hilos, así que todo parece ir viento en popa para AMD.

Por último y centrándonos en escritorio, lo único que sabemos de Vermeer es que las CPUs se encuentran en el stepping B0, por lo que parece que AMD no piensa alcanzar un nuevo upgrade, principalmente porque haces meses que ya vimos dicho step y se mantienen en él. Veremos que termina filtrándose antes de la presentación oficial de estos Ryzen 5000, porque a este ritmo nos van a dejar con el hype hasta el mismo día del pistoletazo de salida.

Fuente: hardzone.es/noticias/procesadores/amd-ryzen-5000-zen-3-cache/