No es ningún secreto que vamos a ver una gama de procesadores Ryzen de AMD basados en Zen 4, y aunque aún falta aproximadamente un año para ello, ya nos podemos hacer una idea de lo que nos va a ofrecer la siguiente generación de la arquitectura Zen de AMD. Es por ello que hemos hecho un pequeño resumen de los cambios que hay confirmados hasta la fecha, basándonos en que el lanzamiento de las CPUs Zen 4 va a coincidir con la llegada del PCI Express de 5ª Generación y la memoria RAM DDR5.

La llegada de los Ryzen 5000 basados en Zen 3 no es la última parada del viaje para AMD, pues ya dijeron una vez que estaban trabajando en Zen 5, por lo que vamos a tener Ryzen para un largo tiempo y no es de extrañar porque esta arquitectura ha sido un cambio de suerte para AMD que le ha dado un giro de 180º en lo que a su situación en cuanto al mundo de los procesadores de PC se refiere.

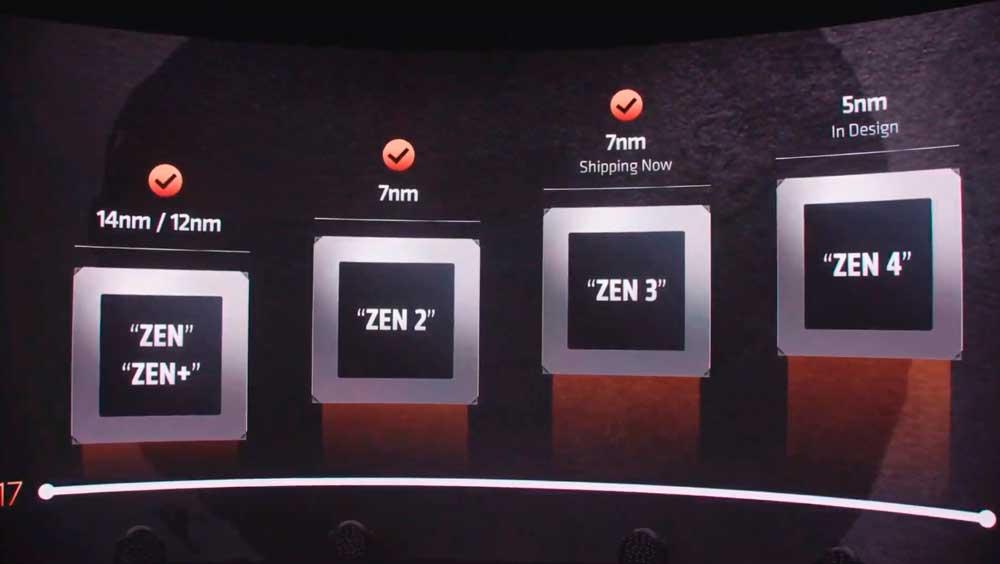

Zen 4 utilizará el nodo de 5 nm de TSMC

Durante la presentación de los Ryzen 5000, AMD confirmó que los chiplets de Zen 4 basados en Zen 4, están diseñados para ser fabricados bajo el nodo de 5 nm de TSMC, por lo que va a suponer un salto equivalente al que hubo con Zen 2 respecto a la primera generación de la arquitectura, ya que fue cuando se produjo el cambio de los 12/14 nm a los 7 nm.

No olvidemos que el nodo de 5 nm de TSMC ya se encuentra totalmente operativo y en estos momentos está siendo utilizado para la fabricación del SoC Apple A14 para el iPhone 12 de los de Cupertino, por lo que empresas como AMD no deberían tardar mucho en poder utilizar el nuevo nodo con tal de empezar la producción de sus procesadores a 5 nm, y en el caso concreto de AMD los chiplets del Zen 4.

Desconocemos por el momento qué cambios con respecto a la arquitectura vamos a ver, pero con el nodo a 5?nm estos deberían ser más profundos que los que hubo con el cambio de Zen 2 a Zen 3 donde pese a las mejoras de rendimiento a nivel de arquitectura, en realidad los cambios han sido mínimos y es posible que veamos un aumento en la cantidad de núcleos y el tamaño de las cachés respecto a Zen 3 aprovechando la mayor densidad del nodo de 5 nm, pero esto es algo que por el momento está en el aire.

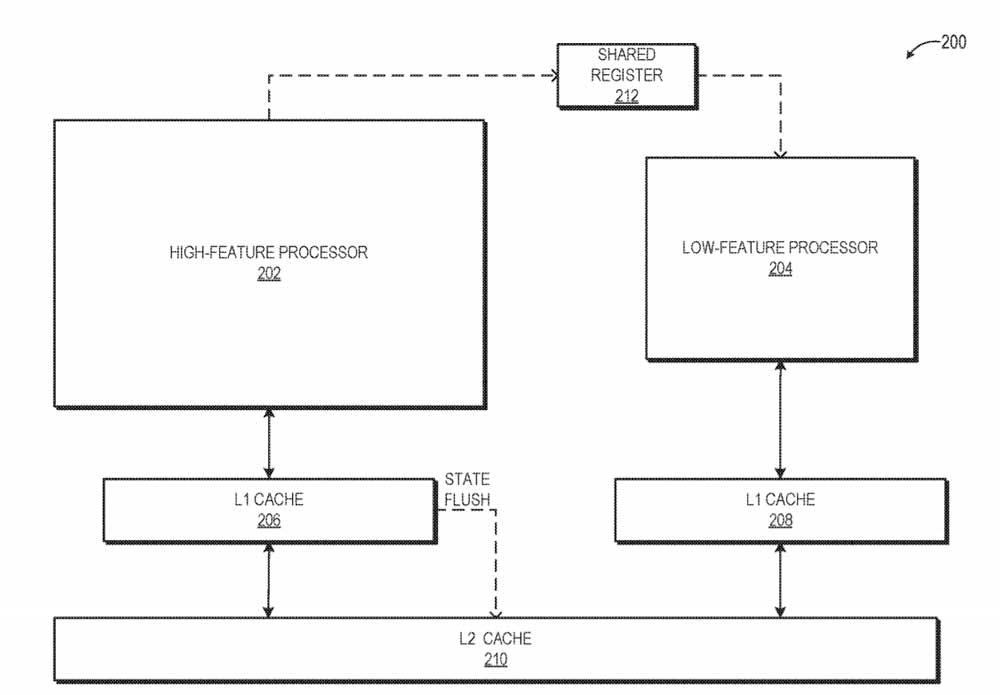

Existen rumores de que AMD podría presentar una arquitectura del tipo “big.LITTLE”, especialmente por una patente que se filtró el pasado mes de agosto que hacía referencia a ello.

La idea es algo distinta al concepto existente en Lakefield de Intel y los núcleos ARM para dispositivos PostPC, ya que en la propuesta de AMD los procesadores de alto y bajo rendimiento estarían no en clústeres separados, CCX o “Core CompleX” cómo los llama AMD, sino dentro del mismo, compartiendo algunos de los registros con caché L1 privada a cada núcleo y la L2 compartida.

La idea detrás de ello sería que el núcleo de bajo consumo se encargue de ejecutar las instrucciones que son mucho más simples, las cuales tienen un consumo energético mucho menor. En todo caso esto no sabemos si esto lo vamos a ver en Zen 4 o en Zen 5, solo que AMD esta experimentando con ello.

El soporte para la memoria DDR5 llegará en Zen 4

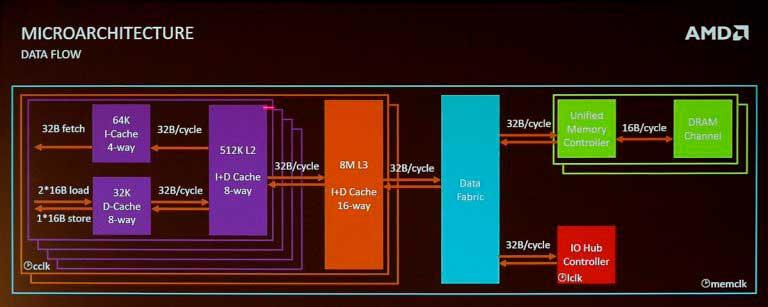

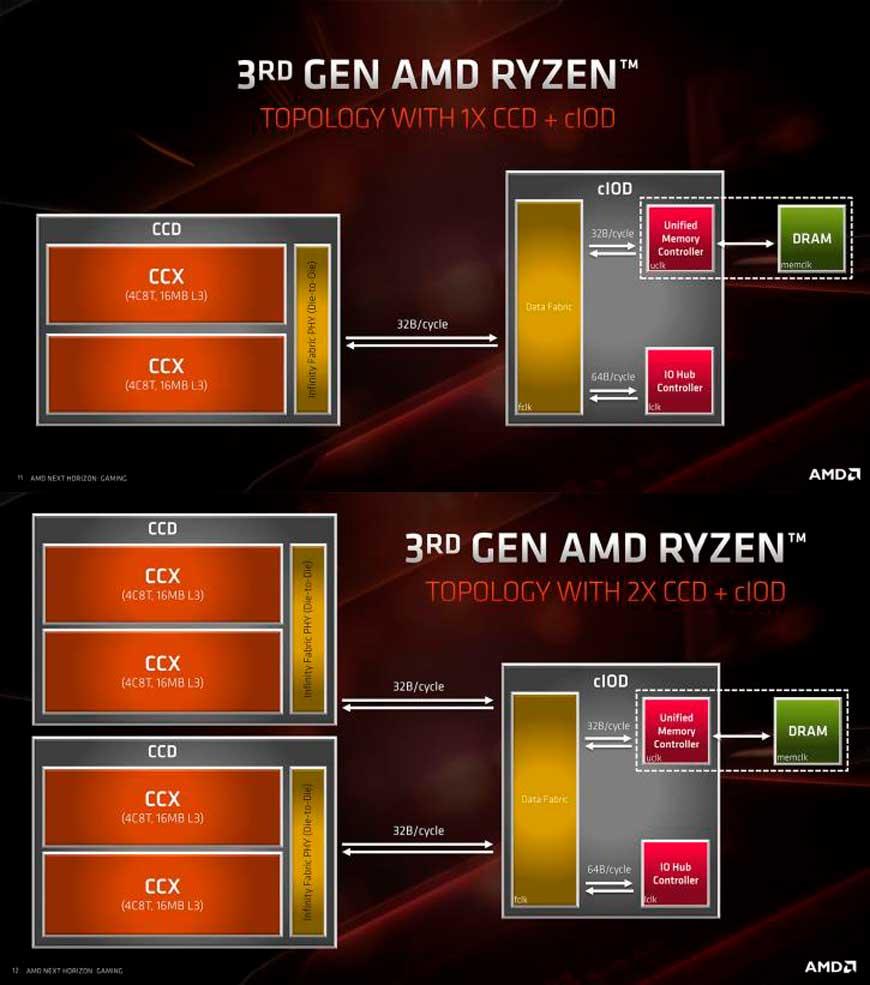

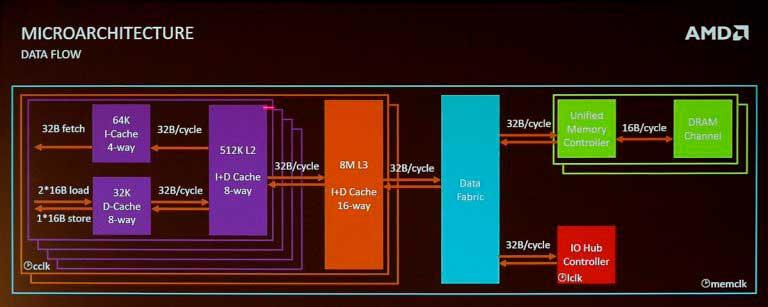

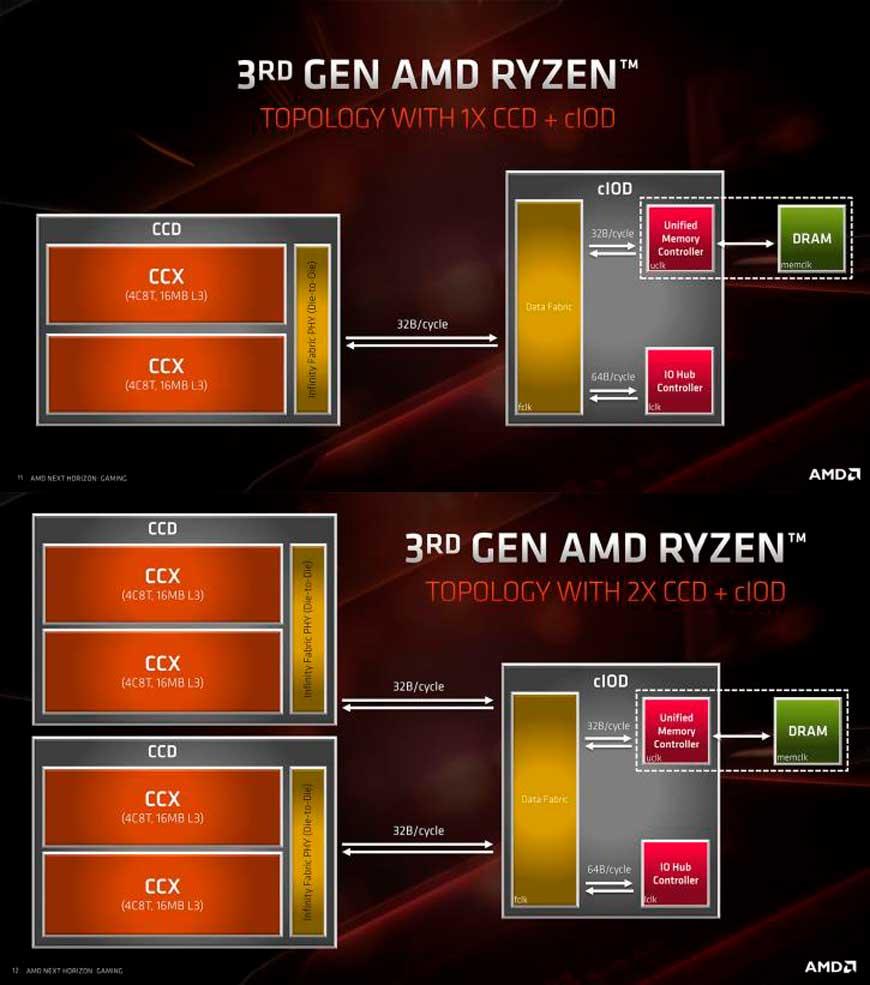

En los procesadores Zen basados en una configuración MCM, módulo de múltiples chips, el chip central es conocido como el IOD o IO Die, en el cual se encuentran tanto el puente norte como el puente sur dentro de la arquitectura.

- El puente norte comunica los núcleos de la CPU y los periféricos con la memoria.

- El puente sur está comunicado al puente norte y maneja los periféricos.

- AMD llama al puente norte Scalable Data Fabric o SDF y al puente sur lo denomina I/O Hub.

Con la llegada de la DDR5 nos encontramos con que AMD va a tener que cambiar por segunda vez toda la parte del acceso a la memoria RAM integrado en el puente norte. La primera vez fue con el SoC AMD Renoir para integrar el soporte para memoria LPDDR4X, pero el cambio a la DDR5 es más profundo debido a que estamos hablando de una RAM cuyos módulos utilizan dos canales de memoria en vez de uno, por lo que el controlador de memoria integrado en el IOD de Zen 4 se tendrá que adaptar a ello.

El uso de memoria DDR5 además significará un cambio en las placas base y es muy probable que AMD adopte un nuevo socket, probablemente el AM5, para los Ryzen basados en Zen 4.

El PCI Express 5.0 será otra novedad importante

El otro cambio importante está en la adopción del PCI Express 5.0, el cual es una mejora incremental respecto a la actual versión 4.0 que duplica el ancho de banda. Como información curiosa, entre el IO Hub y el SDF de los Zen de primera generación que soportan PCIe 3.0 había un bus de 32 bytes/ciclo, en Zen 2 con el soporte para PCIe 4.0 este se duplicó a los 64 bytes/ciclo y con el PCIe 5.0 deberíamos esperar un bus de 128 bytes/ciclo, dado que el ancho de banda se vuelve a duplicar.

Hasta ahora el conector Infinity Fabric que AMD ha utilizado en todas sus arquitecturas ha sido de 32 bytes/ciclo o de 64 bytes/ciclo por lo que AMD de cara a Zen 4 deberá crear un nuevo conector IF para conectar el puente sur con soporte PCIe 5.0 al puente norte.

¿Otros cambios de los que se hablan? Hay rumores de que el IOD podría integrar una caché de último nivel para el procesador, la cual sería un nivel de caché adicional que se situaría entre la cache L3 de los CCX y el controlador de memoria, por lo que estaríamos hablando de una caché L4 propiamente dicha, aunque en todo caso es otro de los elementos que no sabemos si veremos en Zen 4 o en Zen 5.

En todo caso aún nos queda un año como mínimo para ver el siguiente salto de AMD, pero por la poca información que tenemos todo apunta a Zen 4 no va a ser una arquitectura aburrida.

Fuente: hardzone.es/noticias/procesadores/zen-4-ddr5-pcie5/