La perpetuación de la Ley de Moore, la observación de que la densidad de transistores en un chip típico se duplica cada dos años, plantea una serie de desafíos en el nodo de 3 nm; sin embargo, TSMC sigue siendo optimista a pesar de que ven una complicada encrucijada cuando lleguen al nodo de fabricación con litografía de 2 nm. ¿Qué pasará a partir de ahora? ¿Qué dificultades están encontrando?

Hay muchas predicciones que afirman que es probable que la Ley de Moore se de contra un muro más pronto que tarde, pero cómo de pronto está abierto a debate. Existen tecnologías que prometen aumentos continuos en el rendimiento que no dependen de duplicar la densidad del transistor, y la sincronización de todo eso tendrá implicaciones de gran alcance. En el Simposio de Tecnología TSMC 2021 de la semana pasada, el CEO de TSMC, C. C. Wei, dio el ejemplo de los centros de datos, que consumen más del uno por ciento de la electricidad global generada.

TSMC no tiene planes más allá de los 2 nm

«Las estimaciones sugieren que se prevé que el uso global de electricidad de los centros de datos crecerá de cinco a cuarenta veces entre 2010 y 2030. ¿Por qué las proyecciones varían tanto?» – preguntó Wei. “Las estimaciones divergentes se deben en parte a la dificultad de realizar una proyección precisa de nuestra huella. Hay demasiadas variables para considerar, incluso si la Ley de Moore puede continuar».

Las proyecciones pesimistas se basan en la suposición de que la Ley de Moore está llegando a su fin, y las mejoras de eficiencia entregadas por las tecnologías de proceso de semiconductores ya no pueden seguir el ritmo de la demanda de datos y potencia informática, según señala el CEO de TSMC.

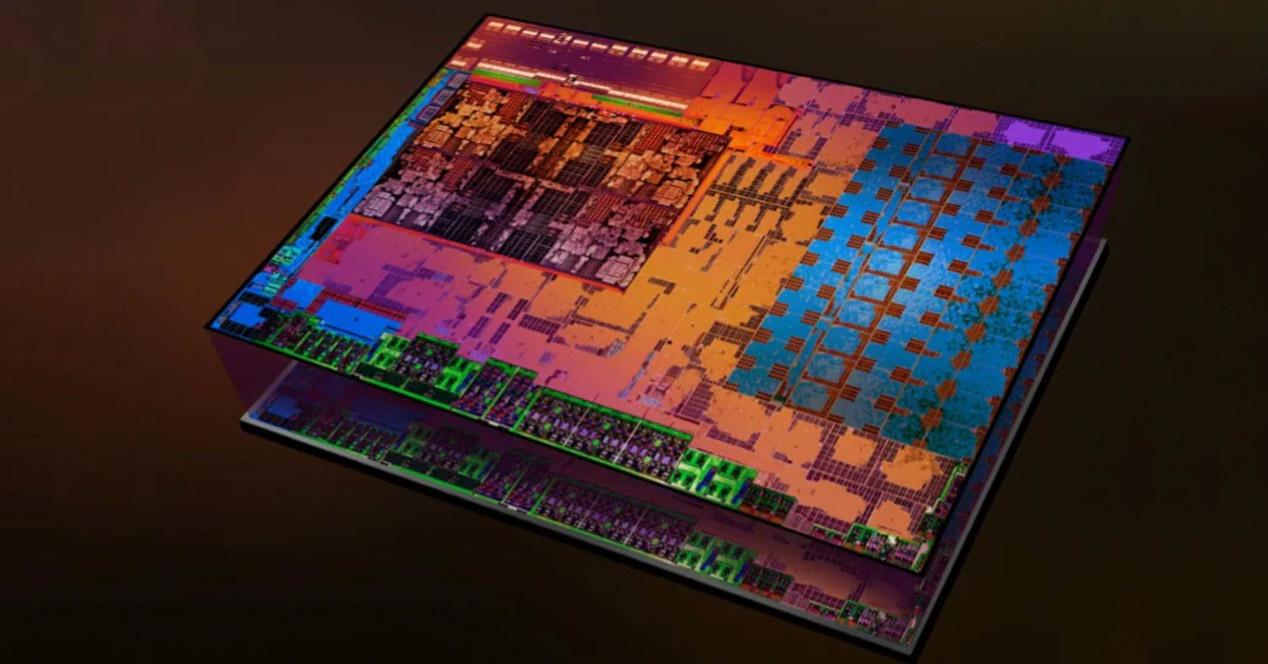

A medida que la hoja de ruta para la reducción del tamaño del silicio de TSMC parece terminar en el nodo de 2 nm; la fundición de semiconductores más grande del mundo está recurriendo a una combinación de tecnologías de empaquetado y el uso de nuevos materiales para mantenerse en el camino de aumentar la densidad de transistores para impulsar el rendimiento y reducir la demanda de energía.

«Tenemos una hoja de ruta predecible y confiable tanto para el escalado 2D como para los IC 3D para perseguir la Ley de Moore y todavía más allá», dijo Wei. «Seguimos ofreciendo la tecnología lógica más avanzada para demostrar que el escalado 2D está vivito y coleando».

La compañía dijo que en este momento, no hay ningún plan para nodos de proceso más allá de 2 nm. En el simposio de tecnología, TSMC ofreció algunos detalles sobre la primera fábrica de 2 nm de la compañía, que se construirá en Hsinchu, Taiwán. Además de proporcionar detalles sobre el lugar donde se construirá, la empresa no dio más detalles sobre un marco de tiempo para la producción o la capacidad.

El cambio de tecnología

Por el momento, se espera que el cambio en la tecnología de procesos para el empaquetado de chips y los nuevos materiales cambie prácticamente toda la producción de chips.

«La industria continúa encontrando nuevas formas de innovar a medida que la Ley de Moore se desacelera», dijo Brett Simpson, analista senior de Arete Research. “La adopción de empaquetados avanzados crea un nuevo paradigma para la industria de los semiconductores, donde los fabricantes de chips y las fundiciones claramente están agregando más valor, y en lugar de vender silicio la industria cada vez venderá más plataformas completas. Creemos que este es un desarrollo crítico en computación en un momento en que los grandes chips monolíticos ya no satisfacen las necesidades de los clientes «.

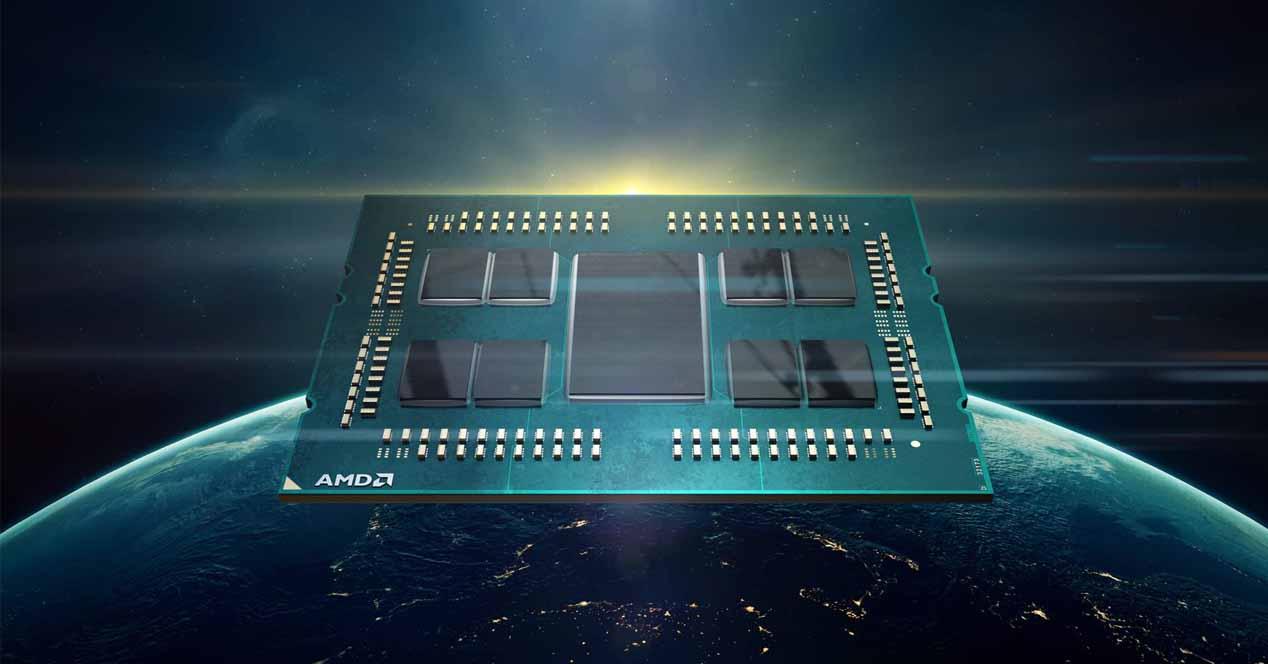

El año pasado, TSMC combinó sus plataformas 3D IC a nivel de oblea bajo un paraguas llamado 3DFabric, que incluye tecnologías frontend y backend, así como la última oferta de TSMC, SoIC (sistema en chips integrados) para apilamiento de silicio. TSMC tiene varias fábricas de backend que ensamblan y prueban matrices de silicio, incluidas pilas 3D, en dispositivos empaquetados. 3DFabric incluye las tecnologías de envasado CoWoS e InFO más antiguas de la empresa.

“Las discusiones recientes en Semicon Taiwan y otros eventos a los que hemos podido asistir han apuntado a 3DFabric como una pieza clave para seguir permitiendo mejoras en el nivel de energía, rendimiento y sistema durante la próxima década a medida que el escalado tradicional se vuelve más técnicamente complicado y costoso”.

De cara a 2022, Wei dijo que SoIC estará listo para la producción en masa y, para fines del mismo año, la compañía tendrá un total de cinco fábricas dedicadas para 3DFabric y, sin embargo, a pesar de que la tecnología avanza seguimos en la tesitura de que por el momento TSMC no tiene planes más allá de los 2 nm (lo cual no significa que, cuando los alcancen, comiencen a planear el escalado a litografías más pequeñas).

Fuente > Eetimes

Fuente: HardZone