La presentación reciente y el lanzamiento inminente de la serie de procesadores AMD Ryzen 5000, basados en la arquitectura Zen 3, ha venido acompañado de la corona para AMD, al menos por el momento, en lo que a potencia se refiere. ¿Pero qué es lo que hace que la arquitectura Zen 3 sea tan rápida? ¿Qué elementos han añadido en la tercera generación de la arquitectura Zen para obtener un mayor rendimiento?

Antes de empezar, hay que tener en cuenta que los Ryzen 5000 no son los sucesores directos de los AMD Ryzen 4000, los cuales son SoCs monolíticos sino del Ryzen 3000, ya que los Ryzen 5000 son también sistemas MCM basados en chiplets.

En dicho sistema, tenemos por un lado el IOD donde se encuentra el Northbridge del sistema, bautizado como Scalable Data Fabric o SDF por AMD y el Southbridge que es llamado IO Hub por la empresa de los Ryzens y las Radeons. Dicho IOD no ha cambiado respecto al del Ryzen 3000 excepto en el hecho de soportar memorias más rápidas ya que es a través del IOD que lo núcleos tienen acceso a la memoria RAM del sistema.

No obstante, no podemos decir que han cogido el IO Die del Ryzen 3000 tal cual y lo hayan trasplantado tal cual, sino que lo han mejorado a través de su experiencia a la hora de crear los Ryzen 4000 para ordenadores de menor consumo que un PC de sobremesa.

Por lo que donde ha habido los cambios realmente importantes es en el CCD o Core Complex Die, que el pequeño chip que almacena los diferentes núcleos y su jerarquía de caches, que es donde ha habido los cambios más importantes.

El nuevo Core Complex Die de la arquitectura Zen 3

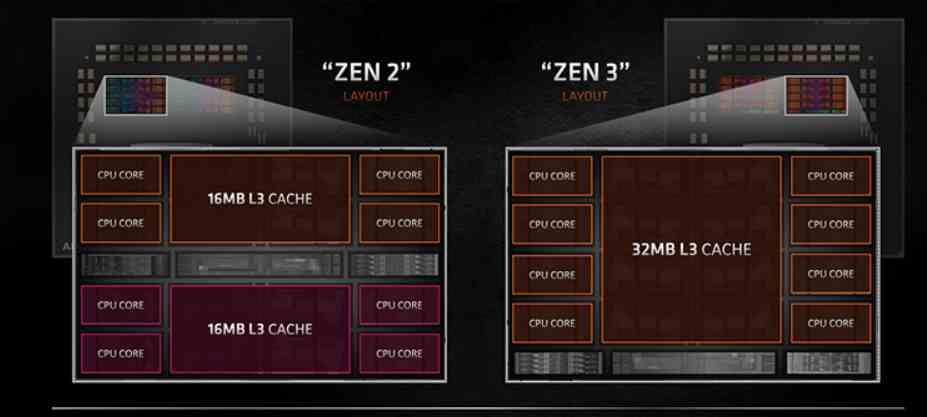

El CCD en Zen 2 estaba compuesto por dos CCX de 4 núcleos cada uno de ellos, con su cache L3 compartida dentro cada uno de los CCX. lo que provoca una serie de problemas de latencia cuando varios núcleos dentro del mismo CCD pero en diferentes CCX se tenían que comunicar, ya que si un núcleo se tenía que comunicar con otro que se encontraba en el otro CCX entonces tenía pasar por el IOD pese a estar en el mismo CCD.

El cambio que ha hecho AMD en la arquitectura Zen 3 es muy simple, han hecho que en vez de 4 núcleos compartan la cache L3 lo hagan 8 núcleos al mismo tiempo. Por lo que hemos pasado de tener 2 CCX de 4 núcleos por CCD a 1 CCX de 8 núcleos por CCD. Esto en aplicaciones pensadas para funcionar con 8 o menos núcleos resulta en una ventaja de rendimiento.

Pero donde AMD ha hecho mejoras a nivel de cada núcleo es en las unidades Load/Store, así como en el front-end o unidad de control, mejoras que han sido clave para conseguir un rendimiento de un 19% de media por encima de su antecesor, Zen 2.

La clave es la unidad de control

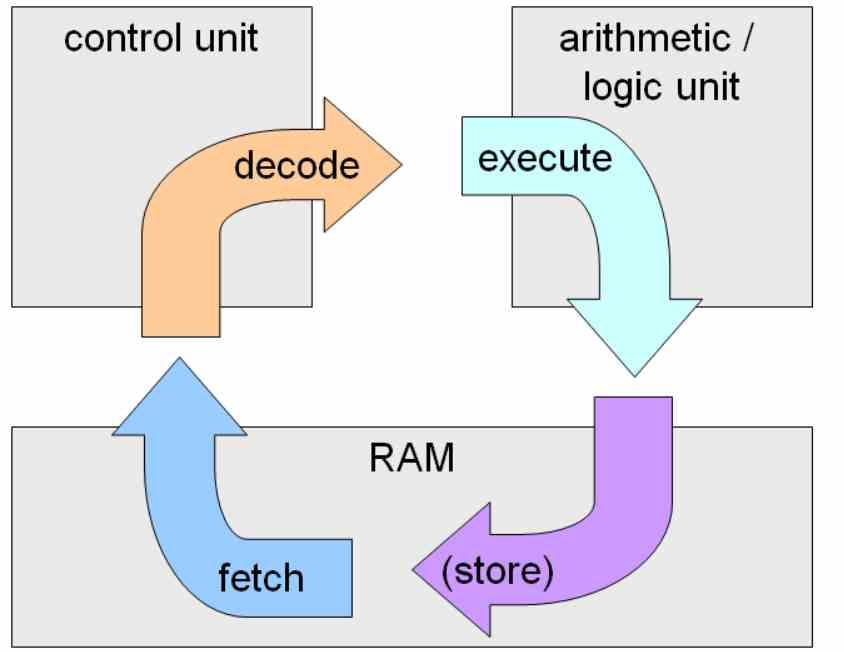

Cuando hablamos de Front-End nos estamos refiriendo a la unidad de control de una CPU, mientras que las ALUs son el Back-end. Dentro del ciclo de instrucción, captar-decodificar-ejecutar, las dos primeras etapas son trabajo de la unidad de control, mientras que la segunda parte son trabajo de las ALUs o unidades de ejecución.

Todos los procesadores x86 contemporáneos no ejecutan las instrucciones bajo dicha ISA, sino que descifran las instrucciones en una ISA RISC interna que es con la que se ejecutan realmente las instrucciones en las unidades de ejecución. Dicha ISA interna puede cambiar incluso entre miembros de una misma arquitectura y es clave a la hora de aumentar el IPC de los procesadores.

Es por ello que AMD ha re-hecho la unidad de control y ha implementado una nueva ISA interna mucho más eficiente que permite realizar las instrucciones en menos ciclos de reloj por instruccón (CPI), haciendo que la media de instrucciones por ciclo aumente con ello.

Fuente: hardzone.es/tutoriales/rendimiento/arquitectura-zen-3/