Es completamente habitual que los diferentes estándares de memoria DDR en toda su vida comercial tengan mejoras con el tiempo, en especial en forma de versiones mejoradas del controlador de memoria que traen consigo una mayor velocidad de reloj y con ello más ancho de banda. RAMBUS acaba de presentar su interfaz para memoria DDR5-5600 para servidores en módulos RIMM. ¿Qué significa esto para Intel y AMD?

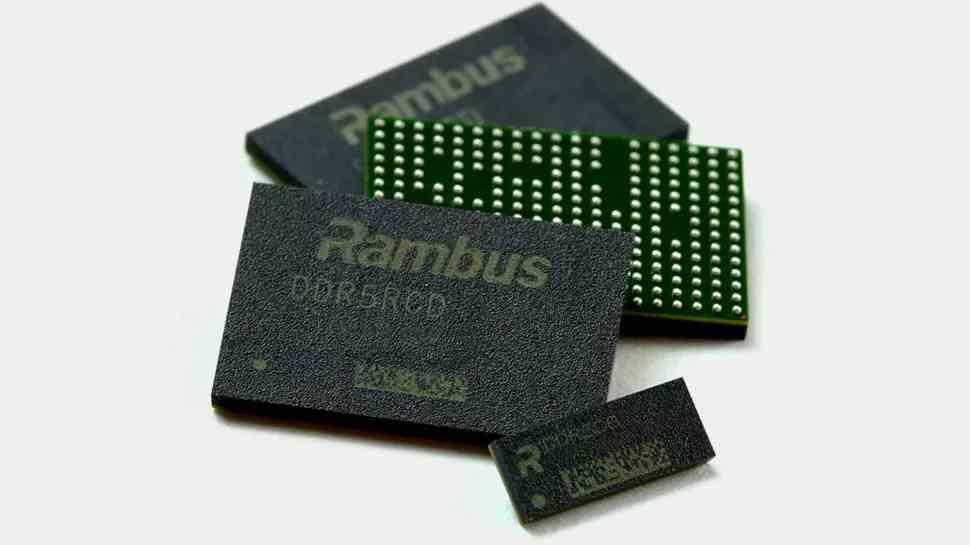

La empresa RAMBUS es una de las veteranas en el mundo del desarrollo de nuevos tipos de memoria RAM, fue famosa en los 90 y principios de los 2000 por sus memorias RDRAM, pero estas perdieron la batalla frente a la DDR y las GDDR. Desde entonces RAMBUS se ha convertido en la diseñadora de interfaces con memoria RAM de todo tipo, las cuales diseña a nivel interno para luego licenciarlas a terceros en forma de archivos en Verilog o VHDL para su fácil implementación por parte de los diseñadores de CPU.

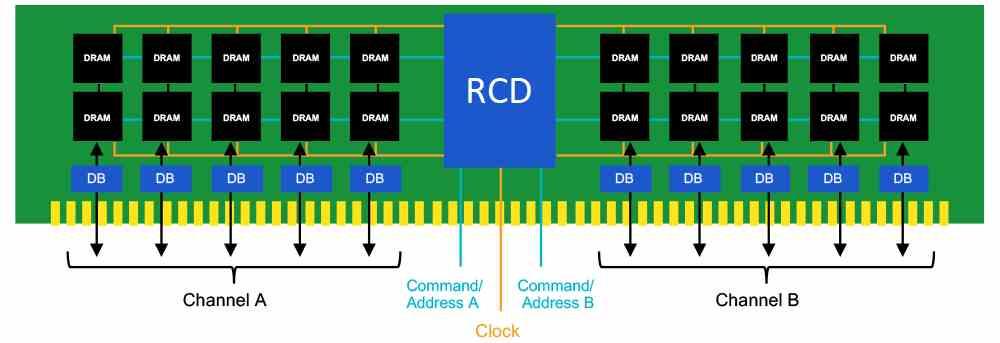

Su última novedad ha sido la presentación de una interfaz DDR5-5600, pero no solo para los módulos DIMM habituales, sino también para los módulos RIMM que se utilizan en servidores. Por lo que futuras generaciones de los AMD EPYC e Intel Xeon podrían implementar este controlador de memoria en su perímetro para comunicarse con la RAM del sistema en la que se encuentran. La otra mitad de la interfaz se coloca como un chip aparte en la parte central de los módulos de memoria RAM, ya sean estos del tipo DIMM, RIMM o cualquier variación de estos.

¿Qué es la controladora DDR5-5600 de RAMBUS?

Realmente la interfaz DDR5-5600 de RAMBUS no tiene nada de especial, no es otra cosa que una controladora para memoria DDR5 o mejor dicho, es la interfaz de hardware que comunica el Northbridge e IMC de la CPU con la memoria RAM. Se trata de una pieza que por cercanía con la RAM y para evitar aumentos de latencia y consumo se coloca en la periferia de todo procesador que la utilice.

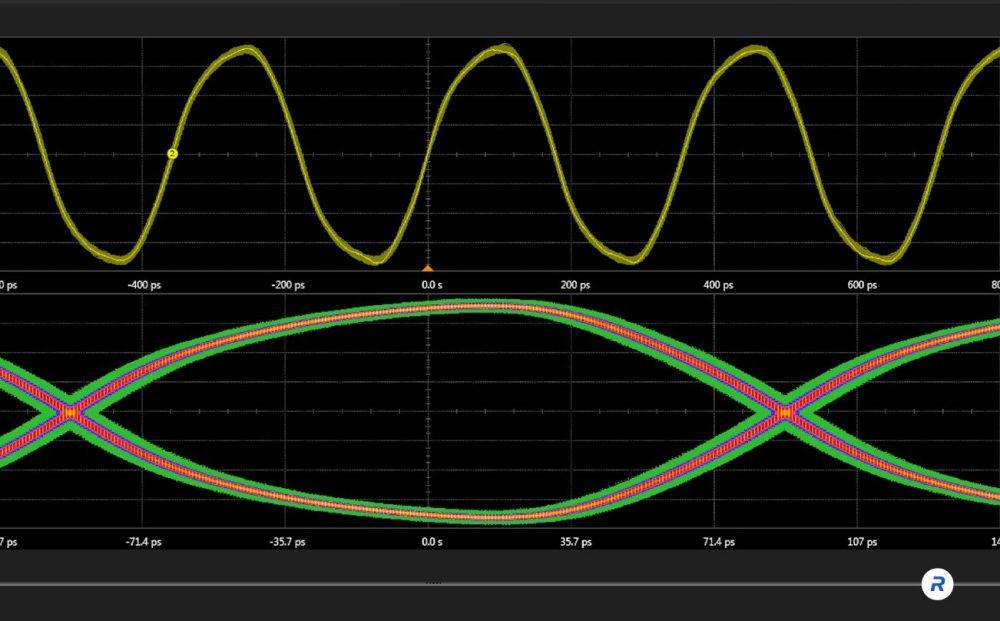

Hasta el momento los controladores DDR5 que ha habido disponibles son DDR5-4800, pero con la llegada del DDR5-5600 de RAMBUS se hace posible la implementación en CPU a corto y medio plazo con soporte para memoria Dual Data Rate de quinta generación. Claro está que al ser un anuncio reciente esto no afectará a CPU como los Intel Core 12 que ya están en producción. En cambio otros procesadores más lejanos que no han entrado todavía en producción final podrían recibir estas interfaces en su diseño.

Es decir, Intel no va a poder implementar en sus nuevas CPU que están a punto de salir esta interfaz de memoria y por lo tanto, sus CPU se quedan en 4800 MHz como JEDEC, mientras que AMD tiene todavía tiempo de lograrlo para Zen 4 y tener con ello una velocidad mínima de los 5600 MHz citados.

No podemos olvidar que un cambio de este tipo puede suponer una serie de cambios adicionales en el diseño del hardware que acompaña a la CPU, ya que supone también variaciones en la placa base y el chipset de la misma, los cuales se diseñan alrededor de las especificaciones del procesador.

Hay que tener en cuenta que ya existe memoria DDR5 a mayor velocidad, pero la particularidad de este controlador DDR5-5600 de RAMBUS no es otro que permitir una relación entre la CPU y este tipo de memoria RAM sin tener que bajar la velocidad de reloj del controlador de memoria en la parte del procesador y aumentar la latencia debido a ello. Dicho de otra manera, las CPU posteriores al Intel Core 12 que utilicen esta interfaz DDR5-5600 de RAMBUS con la memoria de este mismo tipo no necesitarán poner la CPU en modo Gear 2 para usar este tipo de memoria, aparte de no requerir XMP.

Diseñado para módulos RIMM para servidores

No obstante la controladora DDR5-5600 de RAMBUS está diseñada para su uso en módulos RIMM y por tanto veremos su implementación en los Intel Xeon Sapphire Rapids. Los módulos RIMM hacen uso de un búfer que se coloca entre la memoria DRAM misma y el controlador y se encarga de distribuir las señales que incluyen la información de direccionamiento y comandos con el objetivo de tener una mejor integración de la señal. La contrapartida de ello es que aumenta las latencias y como consecuencia se requiere que el controlador flash dentro del módulo RIMM este diseñado para unas velocidades concretas como es el caso que nos ocupa.

Fuente > Guru3D

Fuente: HardZone